Increasing the integrated circuits complexity by lateral scaling, known as Moore’s law, has been the major driving force for the semiconductor industry. Now, after more than 4 decades, new solutions need to be explored to further increase the transistor count, as traditional downscaling strategies are reaching their fundamental limits. One of the most promising directions is to exploit the third dimension in chip architectures.

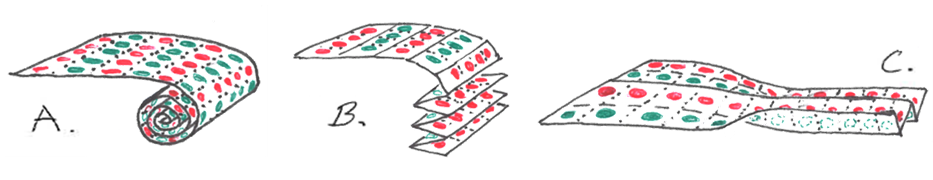

The ORIGENAL project develops a radically new approach to address the challenge of ultra-dense 3D integration of CMOS devices. The key idea is to use a thin-film-transistor (TFT) technology on thin foil substrate, and then fold the substrate to achieve a dense 3D packaging with completely new integration architectures, addressing both traditional logic and neuromorphic computing schemes

The project focuses on the development of

- — a suitable thin-film-transistor technology on ultrathin-foil,

- — tailored 3D interconnects and device architectures,

- — the technology for high precision folding.

ORIGENAL will not only lay the foundations for a new line of technology, but also open up an opportunity to reinforce the technological leadership of European players.